Tales from the Cube: Swan song for swapout strategy Pg 58

> EDN.comment: Can C beat RTL? Pg 4

Signal Integrity: Way too cool Pg 14

Design Ideas Pg 43

Supply Chain Pg 54

EN1

# WIRELESS TO GO

VOICE OF THE ENGINEER

Classi

Page 26

x86 PROCESSORS: CONTINUED INNOVATION IS A WELCOME CONTRADICTION Page 19

Tools accurately simulate noise in MIXED-SIGNAL ASICs Page 33

DEBUGGING AND ANALYSIS WITH SystemVerilog test bench Page 38

#### TO JUMP START YOUR DESIGN, RECEIVE A 50% DISCOUNT ON POWER METERING EVALUATION BOARDS!

DISCOUNT APPLIES TO THE FOLLOWING BOARDS: CDB5461AU, CDB5463U, CDB5464U, CDB5466U, CD5467U HURRY! THIS IS A LIMITED TIME OFFER!

Visit www.cirrus.com/546Xedn

## **High-Precision Family of Power Meter ICs**

CS546X FAMILY DELIVERS UNSURPASSED PERFORMANCE, FEATURES FOR ALL METROLOGY CALCULATIONS

Whether it's single- or three-phase, residential or industrial, metering or monitoring, Cirrus Logic has a family of energy measurement products that are ideal for your needs. Cirrus Logic's CS546X energy management family delivers unsurpassed performance in data accuracy and are fully featured to deliver all required metrology calculations. These products are designed to accurately measure instantaneous current and voltage and calculates VRMS, IRMS, instantaneous power and average power (active/reactive/apparent) for high-performance energy measurement applications.

#### FEATURES

- On-chip functions:

- Energy data linearity ±0.1% of reading over 1000:1 dynamic range

- On-chip energy calculations

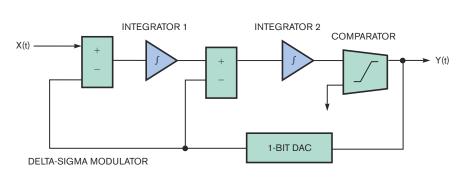

- 24-bit fourth-order Delta Sigma A/D converters for precise measurements

- On-chip 2.5 V reference (tempco 25 ppm/°C typ)

- On-chip energy direction indicator

- 24-pin SSOP package

| Part    | Channels | SPI Slave<br>Interface | Real<br>(Active)<br>Power | IRMS<br>VRMS | Apparent<br>Power<br>(S) | Reactive<br>Power<br>(Q) | Fundamental<br>Power | Temp<br>Sensor | Package |

|---------|----------|------------------------|---------------------------|--------------|--------------------------|--------------------------|----------------------|----------------|---------|

| CS5461A | 2        |                        | $\checkmark$              | $\checkmark$ | $\checkmark$             |                          |                      | $\checkmark$   | 24 SSOP |

| CS5463  | 2        |                        | $\checkmark$              | $\checkmark$ | $\checkmark$             | $\checkmark$             | $\checkmark$         | $\checkmark$   | 24 SSOP |

| CS5464  | 3        |                        | $\checkmark$              | $\checkmark$ | $\checkmark$             | $\checkmark$             |                      |                | 28 SSOP |

| CS5466  | 2        |                        | $\checkmark$              |              |                          |                          |                      |                | 24 SSOP |

| CS5467  | 4        |                        | $\checkmark$              | $\checkmark$ | $\checkmark$             | $\checkmark$             |                      | $\checkmark$   | 28 SSOP |

#### **NORTH AMERICA** +1 800-625-4084

**ASIA PACIFIC** +852 2376-0801

JAPAN

+81 (3) 5226-7757 EUROPE/UK

+44 (0) 1628-891-300

#### . LEARN MORE AT WWW.CITTUS.COM

© 2010 Cirrus Logic, Inc. All rights reserved. Cirrus Logic, Cirrus and the Cirrus Logic logo designs are trademarks of Cirrus Logic, Inc All other brands and product names may be trademarks or service marks of their respective owners. EDN242010

# Authorized distributor for more than 440 of the world's most trusted manufacturers.

THE INDUSTRY'S BROADEST PRODUCT SELECTION AVAILABLE FOR IMMEDIATE DELIVERY.

#### 1.800.344.4539 WWW.DIGIKEY.COM

\*Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2010 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

Supplier Authorized Distributors

#### Wireless to go

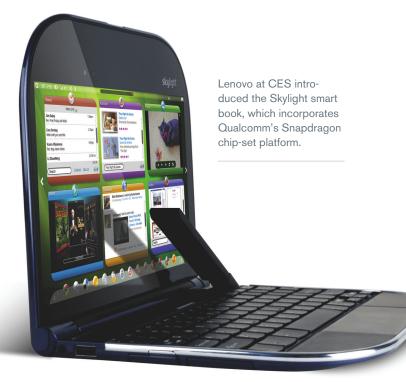

26 Vendors are serving up a variety of hardware and software flavors to add communications capability to fixed and mobile devices. by Rick Nelson, Editor-in-Chief

#### x86 processors: Continued innovation is a welcome contradiction

19 Although the last several years have seen much constriction within the semiconductor industry, development and implementation activities in the PC area have remained comparatively bullish. Vendors of x86 processors have various plans for continuing this trend.

by Brian Dipert, Senior Technical Editor

# DUISE Dilbert 9

- 8 NI pursues robot revolution

- 9 3-D medical printer to print body parts

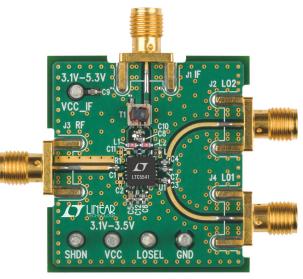

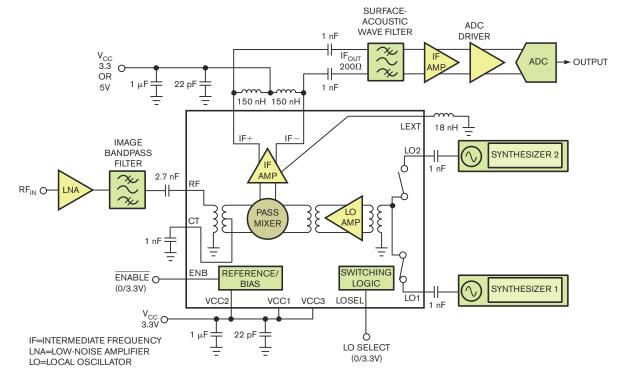

- 10 3.3V mixer downconverts RF with good linearity

- 11 Affordable scope family now includes four-channel and 40-MHz models

- 11 Blackfin targets lower BOM costs

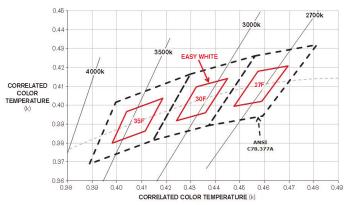

- 12 Tighter binning yields more consistent HB LEDs for indoor apps

- 12 Open-Silicon adds Silicon Logic Engineering

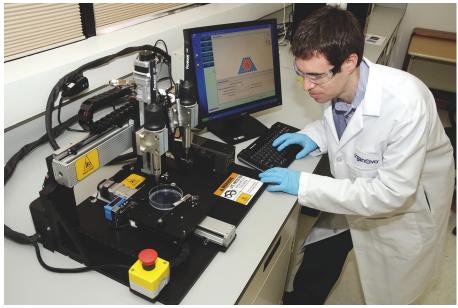

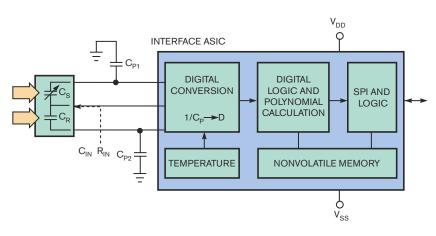

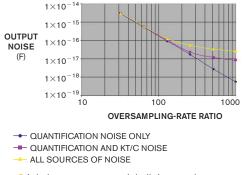

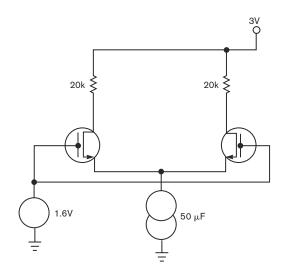

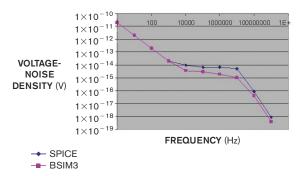

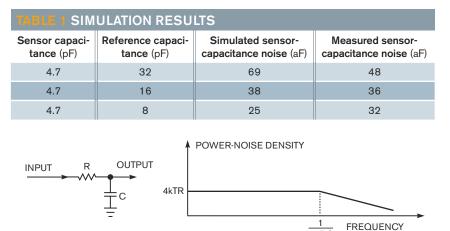

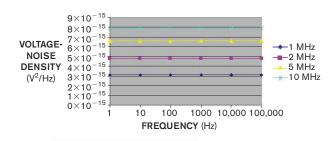

#### Tools accurately simulate noise in mixed-signal ASICs

33 In applications requirting high precision, getting noise estimates right means understanding both the application and the tools.

> by Thierry Masson, Laurent Monge, and A Glascott-Jones, e2v

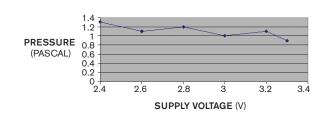

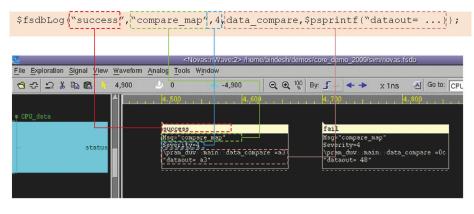

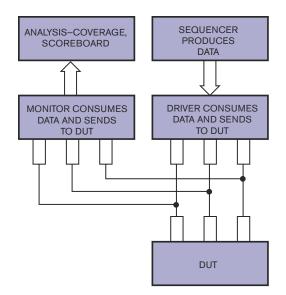

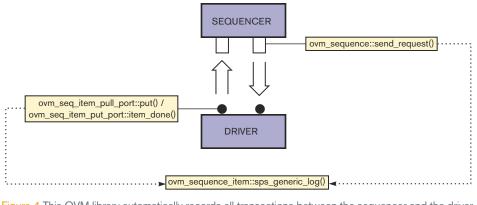

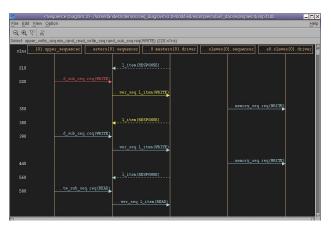

#### Debugging and analysis with System-Verilog test bench

3800 minor additions to New world of visibility for design verifiers. by Bindesh Patel and Rex Chen, SpringSoft

## DESIGNIDEAS

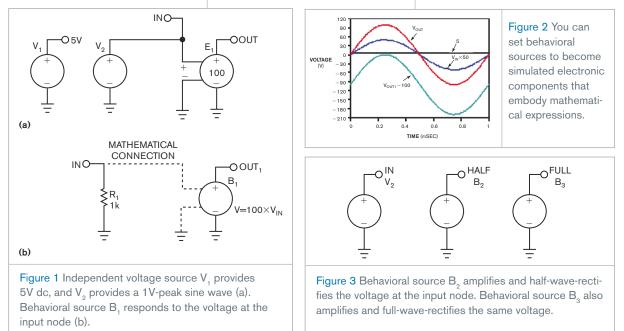

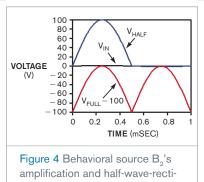

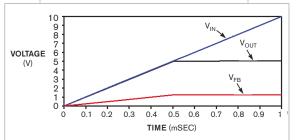

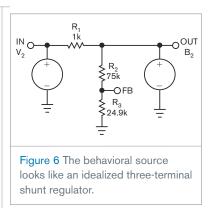

43 Spice simulators provide behavioral sources to mere mortals

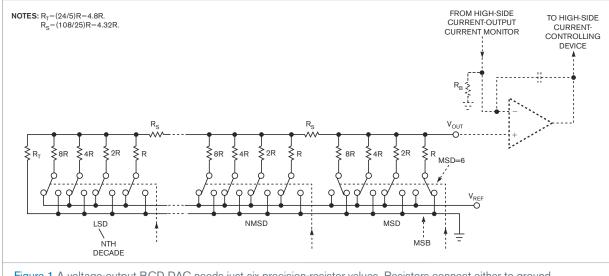

44 Multidecade BCD DAC uses resistors of only six values

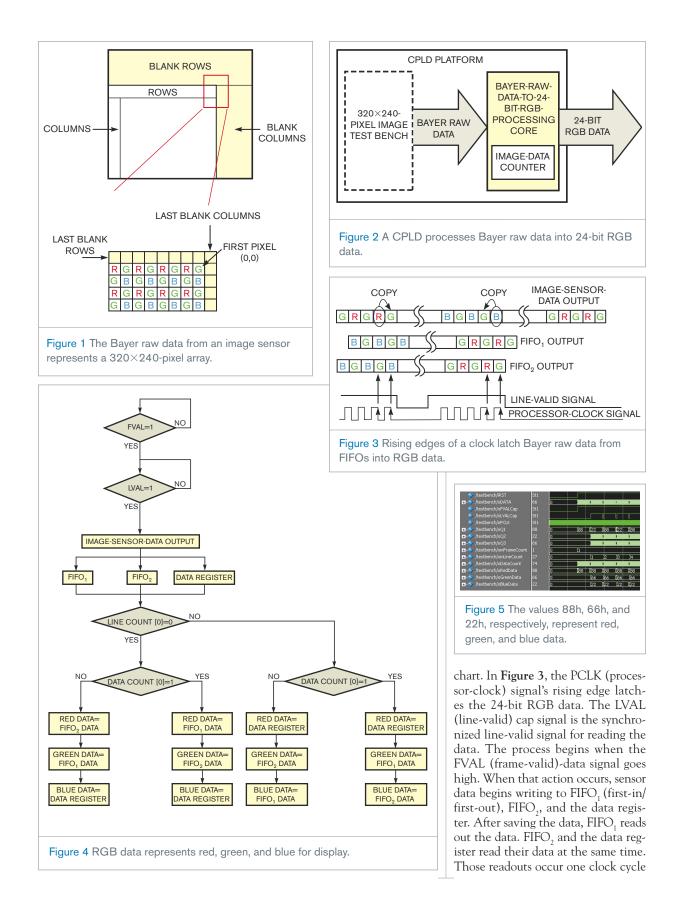

47 Converter translates Bayer raw data to RGB format

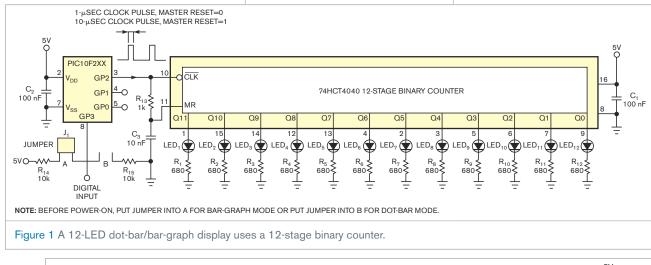

50 Drive 12 LEDs with one I/O line

52 Circuit precludes common-mode conduction

#### **DEPARTMENTS & COLUMNS**

- 4 EDN.comment: Can C beat RTL?

- 14 Signal Integrity: Way too cool

- 16 Mechatronics in Design: Looking beyond STEM

- 54 **Supply Chain:** NEDA targets counterfeit components with return guidelines; Mobile-CE-device shipments to increase 55-fold; DOE introduces lighting-facts label

- 56 Product Roundup: Passives, Integrated Circuits

- 58 Tales from the Cube: Swan song for swap-out strategy

#### **EDN**) online contents

#### ONLINE ONLY

Check out this Web-exclusive article:

#### Determine your IC's transient thermal behavior to prevent overheating

Use Spice to determine the thermal time constants of the IC package. → www.edn.com/article/CA6713633

#### INNOVATION AWARDS

Mark your calendar. *EDN* will announce the Innovation Award finalists online and in print Feb 18. No campaign speeches, attack ads, or empty promises—just recognition for worthy engineers and innovative products.

→www.edn.com/innovation

#### FOLLOW THE DOTTED LINES

www.edn.com

When visiting EDN.com, you may run across special links that have a dotted underline. Unlike other sites that use such links to trick you into viewing advertising, we're using them to lead you to our Hot Topics pages, where you'll find copious links to information from not only *EDN* but also the entire electronics-industry Web. Follow a dotted link, or visit the Hot Topics home page. →www.edn.com/hottopics

#### News and New Products LabView 8.6 adds wireless, enhances multicore and FPGA features Number News Test & Massurement Wood - EDN, 9/18/2008

National instruments currents of the second second

ng these technologies, you can develop a wireless-sensor network and control it with LabView. I can also download drivers for numerous proprietary wireless-sensor networks, and, using the View Wireless Toolkit, you can test wireless devices that use any of these technologies.

EDN & (ISSN#0012-7515), (GST#123397457) is published semimonthy, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. John Poulin, CEO/CFO, RBI-US; Jeff DeBalko, President, Business Media; Jane Volland, Vice President, Finance. Periodicals postage paid at Littleton, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN & PO Box 7500, Highlands Ranch, CO 80163-7500. EDN & copyright 2010 by Reed Elsevier Inc. Rates for nonpualified subscriptions, including all issues: US, \$179.99 one year; Canada, \$229.99 one year; Canada, \$229.99 one year; Canada, \$229.99 one year; air expedited, \$399.99 one year; Canecial sizues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN & R878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN & is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 55, Number 3 (Pinted in USA).

# IR's IRF6718 Delivers Industry's Lowest R<sub>DS(ON)</sub>\*

#### **Features**

- Industry Lowest R<sub>DS(on)</sub> for reduced conduction losses

- Superior electrical and thermal performance in smaller footprint than D<sup>2</sup>Pak

- Dual-sided cooling compatible

- Reduces component count and board space compared to competing solutions

- Compatible with existing Surface Mount Techniques

- RoHS compliant containing no Lead or Bromide

| Part<br>Number | Package<br>Size<br>(mm x mm) | R <sub>DS(ON)</sub> @ 10V<br>typ. (mΩ) | I <sub>p</sub> @TA = 25°C<br>(A) |  |

|----------------|------------------------------|----------------------------------------|----------------------------------|--|

| IRF6718        | 7.1 x 9.1                    | 0.5                                    | 270                              |  |

| Competitor 1   | 10.7 x 15.9                  | 0.7                                    | 180                              |  |

| Competitor 2   | 5.1 x 6.1                    | 0.95                                   | 60                               |  |

| Competitor 3   | 5.1 x 6.1                    | 1.5                                    | 65                               |  |

\* Based on data complied September 2009

For more information call 1.800.981.8699 or visit www.irf.com

#### BY RON WILSON, EXECUTIVE EDITOR

# Can C beat RTL? ith the appearance of higher speeds and more DSP macrocells in low-cost FPGAs, more and more design teams are seeing the configurable chips not as glue but as a way to accelerate the inner loops of numerical algorithms, either in conjunction with

or in place of the traditional DSP chip. There's a problem, however. You code for a DSP chip in C, and you implement it using a conventional software tool chain with familiar software debugging tools. You configure an FPGA starting in Verilog or VHDL (veryhigh-speed-integrated-circuit-hardware-description language)—superficially similar to C but in practice profoundly different—and you implement it using a hardware design flow. The two approaches require different skills.

Enter ESL (electronic-system-level) tools. An ESL synthesis tool lets you write your code in C, automatically synthesize RTL (register-transfer-level) logic from the C, and then feed the RTL into your FPGA flow. In reality, such tools meet with skepticism because people suspect them of poor quality of results, unreliability, and other vices. Is that assessment fair, though? BDTI (Berkeley Design Technology Inc) wanted to find out.

The company last month released the first results of its certification program for high-level synthesis tools. The first evaluation covers AutoESL's AutoPilot and Synfora's Pico. The bottom line in BDTI's findings was that both tools produced results in a reasonable amount of time and that both performed much better than software on a DSP chip. The tools were comparable in density and performance with hand-coded RTL. The fine print reveals a wealth of information below that level, however.

#### It is no longer prudent for design teams working with computationally oriented cores to ignore ESL synthesis tools.

First, BDTI uses a method that represents, as always, a compromise between realism and practicality. BDTI's initial benchmark is a fully functional optical-flow design comprising a three-ring binder and a DVD, which in turn contain a text description of the algorithm, the algorithm in about 600 lines of ANSI C, and a Xilinx reference design. BDTI turns the kit over to the ESL vendor, which tunes the C code for the tool and produces a design. BDTI engineers then independently repeat the process. The optical-flow core attempts to achieve maximum throughput using all the resources available in the Spartan IIIA FPGA.

Unsurprisingly, both ESL vendors produced designs with about 40 times the throughput of the best BDTI engineers could do on a Texas Instruments DM6437 DSP chip. Surprisingly, in a separate test with a smaller design, results from the ESL flows required essentially the same die area as a hand-coded RTL kernel.

The amount of work to do the FPGA design, from C to programming file, was similar to the work to program the DSP, according to Jeff Bier, BDTI president. Significant differences between the two tasks emerged, however, Optimizing the C code for one of the ESL tools caused the code to balloon from the original BDTI-supplied 559 lines to 1604 lines of C. Bier says that the work in the optimization was somewhat less than optimizing the code for the DSP chip. "It turned out that the DSP had a serious memory bottleneck that we had to code around," he explains. The synthesis tool then generated more than 38,000 lines of Verilog from the optimized C.

BDTI engineers, experienced DSP programmers, could handle the entire flow for the TI chip. A huge pile of Verilog and a stack of Xilinx tools stumped them, though. They ended up calling in an RTL-logic expert to shepherd the RTL through the Xilinx tool chain, debug it, and produce the configured FPGA.

Clearly, it is no longer prudent for design teams working with computationally oriented cores to ignore ESL synthesis tools. The analogy to the days when RTL synthesis was just beginning to displace schematic capture and Karnaugh maps or, for that matter, when programmers began to write embedded software in C instead of assembler is irresistible. Stand by for change.EDN

Contact me at ronald.wilson@reed business.com.

#### PRESIDENT, BUSINESS MEDIA, REED BUSINESS INFORMATION

Jeff DeBalko, jeff.debalko@reedbusiness.com 1-646-746-6573

PUBLISHER, EDN WORLDWIDE Russell E Pratt, 1-781-734-8417;

rpratt@reedbusiness.com ASSOCIATE PUBLISHER, EDN WORLDWIDE Judy Hayes, 1-925-736-7617;

judy.hayes@reedbusiness.com EDITOR-IN-CHIEF, EDN WORLDWIDE Rick Nelson, 1-781-734-8418;

rnelson@reedbusiness.com **EXECUTIVE EDITOR** Ron Wilson, 1-510-744-1263; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Amy Norcross 1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

> SENIOR ART DIRECTOR Mike O'Leary

1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

#### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

#### MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

NEWS

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

DESIGN IDEAS EDITOR Martin Rowe, Senior Technical Editor, Test & Measurement World edndesianideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-303-265-3131; f.granville@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION Diane Malone, Manager

1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney, Production/Editorial Coordinator 1-781-734-8442; fax: 1-303-265-3198 Melissa Annand, Web Operations Specialist

1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

> CONSULTING EDITOR Jim Williams, Staff Scientist, Linear Technology

#### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

#### PRODUCTION

Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

#### EDN EUROPE Graham Prophet, Editor, Reed Publishing +44 118 935 1650; aprophet@reedbusiness.com

EDN ASIA Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

#### **EDN CHINA** William Zhang, Publisher and Editorial Director

wmzhang@rbichina.com.cn Jeff Lu, Executive Editor jefflu@rbichina.com.cn

#### EDN JAPAN Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.geffreemag. com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# **NAXING RELIABILITY** In contact, stability and low noise performance

Mill-Max Mfg. Corp. spring-loaded connectors provide superior reliability under the most rigorous environmental conditions, offering: \_\_\_\_\_\_

- Continuous, low-noise electrical connections.

- Spike-free stability to 50G shock and 10G vibration.

- Continued high performance

- through 1,000,000+ cycles.

- Low- and high-profile surface-mount styles.

- 45 discrete designs for customer-specific assemblies.

- 6 families of single and double strip assemblies.

- The shortest production lead times in the industry.

SLC Connector Assemblies

#### Stay in contact with Mill-Max spring-loaded connectors.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit

www.mill-max.com/EDN596

A MALFUNCTION IN THE SYSTEM **COULD COST THE PLANT MILLIONS...**

THE EMBEDDED

THEY'RE COUNTING ON ME TO DELIVER.

AND HAVE THE CONNECTIVITY TO TRACK PERFORMANCE IN REAL TIME.

WINDOWS® EMBEDDED OFFERS A HIGHLY RELIABLE PLATFORM, WITH THE LEVEL OF PERFORMANCE YOU NEED TO HELP DELIVER CONNECTED DEVICES THAT STAND OUT.

WHICH WINDOWS EMBEDDED PLATFORM CAN HELP YOU DELIVER STANDOUT DEVICES? FIND OUT AT WINDOWSEMBEDDED.COM/DEVICESTORIES

#### **INNOVATIONS & INNOVATORS**

#### NI pursues robot revolution

ational Instruments is moving aggressively to support the "robot revolution" with its announcement of LabView Robotics 2009, which provides a standard development platform for designing robotic and autonomous control systems. With the new release, the company hopes to capitalize on what it forecasts is a burgeoning market for robots, including the fact that one-third of US military vehicles must be autonomous by 2015, representing a \$52 billion market. Further, the educational-robotics market will reach \$1.96 billion by 2014. And, by 2012, service robots for professional use will increase 78%, service robots for household use will increase 109%, and robots for entertainment and leisure will increase 239%.

With LabView for Robots 2009, NI aims to overcome the challenges that currently limit robot usage in our day-to-day lives. Those challenges span software design involving modeling, simulation, and algorithm design; embedded-system design involving analog and digital I/O, protocols, motion control, concurrency, and determinism; and connectivity dealing with actuators, sensors, and motors. The company positions LabView as a key tool in meeting that challenge and has received support for that position from David Barrett, PhD, director of SCOPE (Senior Capstone Program in Engineering) at the Franklin W Olin College of Engineering (Needham, MA) and former vice president of engineering at iRobot. Barrett, who delivered a keynote address at last summer's NIWeek, says that the robotics industry requires an industrial-grade, hardened, richly supported software-development system, noting that LabView may well fit that description.

The LabView for Robots 2009 release takes aim at making sure LabView fits Barrett's description, delivering an extensive robotics library with connectivity to standard robotic sensors and actuators, foundational algorithms for intelligent operations and perception, and motion functions for robots and autonomous vehicles. The release ties together LabView's Real-Time, FPGA, Vision, Control Design and Simulation, SoftMotion, Statechart, and Mathscript RT tools as well as the PID (proportional-integral-derivative) Toolkit. It adds robotics IP (intellectual property) for sensing, connectivity, protocols, path planning, obstacle avoidance, and steering. Target hardware platforms include NI's CompactRIO, Single-Board RIO, and a new LabView robotics starter kit.

NI is collaborating with Cogmation on system simulation, Energid on kinematics, Hokuyo on LIDAR (laser-imaging-detection-and-radar) sensors, iRobot on hardware integration, Microsoft on system simulation, MobileRobots on hardware integration, MaxonMotors on smart-motor connectivity, Pitsco on OEM and academic starter kits, Skilligent on vision software, TORC Technologies on the JAUS (Joint Architecture for Unmanned Systems) protocol, and Velodyne on LIDAR sensors.

The base price for a robotics starter kit, including a 180-day evaluation of the LabView robotics-software bundle, is \$1999, or \$1599 for academic customers.—by Rick Nelson ▷National Instruments,

www.ni.com.

#### FEEDBACK LOOP "Been there, done that!! And d\*\*n does it feel good when you kick its behind."

-Engineer Jeff Droll, in EDN's Feedback Loop, at www.edn. com/article/CA6625453. Add your comments.

NI offers a robotics starter kit that includes the DaNI robot and a robotics-software bundle.

THROTTLE

#### 3-D medical printer to print body parts

Researchers hope to custom-build tissues and organs for transplant, using the patient's own cells and a 3-D medical printer (courtesy Invetech).

t the December Printed Electronics USA conference (www.idtechex. com/printed electronicsusa 09), vendors showcased printable batteries, OLED (organic light-emitting-diode) displays, and diabetes-treatment and drug dispensers. One of the most notable technologies on display comes from biosciences company Organovo, which just took delivery of the 3-D medical printer that it designed with Invetech, a design and contract-manufacturing company. The technology "prints" artificial blood vessels for trans-

plant with the goal of creating an arterial graft for use in coronary-bypass surgery. The long-term goal, according to an article in *Information Week*, is to solve problems in medical therapy that other approaches cannot solve (**Reference 1**).

The printer allows researchers to precisely place cells into a 3-D pattern. The technology works by using a robot to lay down cells in precise positions in three dimensions, accurate to within 20 microns. It's similar to the way a laser printer prints by putting solid particles in place. The 3-D medical printer puts objects onto 2-D layers, one on top of the other. The particles comprise stem cells, formed into tiny spheres and cylinders.

"The stem cells are available for research purposes from companies including Life Technologies and Invitrogen," according to the article. Cells, such as bone marrow or fatty adipose tissues, will come from the patient, from which researchers can harvest stem cells. Because the cells come from the patient, there's no risk of rejection. The arterial segments are 5 to 20 cm long, with an interior diameter of 0.5 to 5 mm. Researchers can build arteries with larger interior diameters using Teflon or Dacron, but the smaller diameters clot with synthetic materials."

Like Organovo's equipment, other 3-D printers typically use plaster, cornstarch, or resins to create objects and most often find use in rapid prototoyping for the footwear, jewelry, industrial-design, architecture, automotive, aerospace, dental, and medical industries. Organovo is not alone in finding medical applications for 3-D printing; researchers at the University of Tokyo Hospital (www.h.u-tokyo.ac.jp) and venture company Next 21 are using 3-D printers to create artificial bones for reconstructive surgery.

Oganovo is building blood vessels at first, including an arterial structure for use in coronary-bypass surgery. That procedure involves creating an object with endothelium cells on the inside, smooth muscle in the middle, and an exterior layer of fibroblasts, which are similar to skin cells. Printed blood vessels should be in clinical trials in three to five years, according to the article.-by Margery Conner **⊳Invetech**, www.invetech. com.

**Organovo**, www.organovo. com.

REFERENCE Wagner, Mitch, "3D Printer Builds Artificial Blood Vessels," *Information Week*, Dec 23, 2009, www.informationweek. com/news/healthcare/ patient/showArticle.jhtml; jsessionid=VVBNRPNXY DM2LQE1GHOSKH4AT MY32JVN?articleID=222 003031.

#### **DILBERT By Scott Adams**

# pulse

### 3.3V mixer downconverts RF with good linearity

inear Technology Corp's new LTC5541 downconverting mixer operates at frequencies of 1.3 to 2.3 GHz, and the company plans to later introduce pin-compatible parts that will operate at 0.6 to 4 GHz. The device operates from a 3.3V supply and consumes 630 mW of power during operation and 500  $\mu$ A in shutdown mode.

You can power the IF (intermediate-frequency) amplifier with 5V to improve 1-dB gain compression, and using a local oscillator with a frequency of 1.4 to 2 GHz improves performance. The mixer can switch between two local-oscillator inputs, which function with a drive level of 0 dBm (decibels referenced to milliwatts); both stay at  $50\Omega$  impedance during shutdown so that PLL (phase-locked-loop) circuits remain

An evaluation board for the LTC5541 allows you to assess its performance in your system.

locked. The part achieves an IIP3 (input third-order-intercept point) of 26 dBm, a noise figure of 9.6 dB at 1.95 GHz, and a conversion gain of 7.8 dB at 1.95 GHz.

The mixer finds use in both the main- and the predistortion-

receiver paths. Typical applications include LTE (long-term evolution) and CDMA (codedivision-multiple-access) wireless base stations and WiMax (worldwide-interoperability-for-microwave-access), WCDMA (wideband-CDMA), UMTS (universal-mobile-telecommunications-system), and EDGE (enhanced-data-ratesfor-global-system-for-mobilecommunication evolution) systems. You can also use it for backhaul wireless service between base stations and public-safety and military-communications systems.

The LTC5541 operates at a −40 to +85°C junction temperature; comes in a 5×5-mm, 20-pin QFN package; and sells for \$6.50 (1000). Production has begun.**–by Paul Rako** ▶**Linear Technology Corp**, www.linear.com.

The Linear Technology LTC5541 mixer features good linearity and low noise despite the fact that it operates off 3.3V.

#### BLACKFIN TARGETS LOWER BOM COSTS

04

Analog Devices' new Blackfin BF50x processors operate as fast as 400 MHz, have dual MAC (multiply/accumulate) units, and sell for as low as \$4.50 (10,000). The BF504F adds 4 Mbytes of stacked, parallel flash memory for prices as low as \$6.50, and the BF506F adds dual 12-bit. 2M-sample/second SAR (successive-approximation-register) ADCs and stacked flash for prices as low as \$10.60 (10.000).

All three processors include dual three-phase PWMs (pulse-width modulators), SPIs (serial-peripheral interfaces), SPORTS (space-power radio-transmission systems), and UARTs (universal asynchronous transmitters/receivers) with flow control. They also feature CAN (controller-area-network) interfaces and removable storage interfaces that support SDIO (secure digital input/ output), eMMC (embedded multimedia card), and **CE-ATA** (consumer-electronics advanced-technology attachment).

The BF504 and BF504F are available in 88-pin, 12×12-mm, 0.5-mm LFCSPs, and the BF506F comes in 120-lead, 14×14mm, 0.4-mm LQFPs. The \$199 BF50x Ez-Kit Lite and the \$150 ICE (in-circuit emulator)-100B Blackfin provide support. For more, go to www.edn.com/ article/CA6715679.

-by Robert Cravotta

Analog Devices, www.

analog.com.

# Affordable scope family now includes four-channel and 40-MHz models

eCroy Corp has announced the expansion of its affordable Wave-Ace oscilloscope line to include four-channel models with bandwidths of 60, 100, 200, and 300 MHz and is adding a two-channel, 40-MHz-bandwidth model. The four-channel models provide waveform memory of 10,000 points/ channel, or 20,000 points/ channel when you interleave pairs of channels. They acquire as many as 2G samples/sec/ channel with interleaving. The 40-MHz model acquires 4000 points/channel and as many as 500M samples/sec/channel.

All models offer color displays, extensive measurement capabilities, and advanced triggering to improve troubleshooting and shorten debugging time. The streamlined user interface supports 11 languages. With USB (Universal Serial Bus) host and device ports and a LAN connection, the instruments allow remote control and let you easily save data to a memory stick, PC, or printer.

The 20,000-point memory

#### Buttons are backlit so you don't have to guess at the scope's operating mode.

enables the full-sample-rate capture of waveforms whose length is as much as three times that of waveforms you acquire with similarly priced competitive units. With 32 built-in automated measurements, including advanced modes for skew, phase, and channel-to-channel edge timing, the scopes simplify waveform analysis. Such features as pass/fail testing, user-definable digital filters, and a waveform-sequence recorder simplify and shorten debugging.

A new remote-control command set makes the four-channel models even more versatile than their predecessors. This command set provides access to all of the controls, functions, and measurements from a remote PC through the rearpanel LAN or USB-host ports. These connections also allow you to view the waveform display and access a virtual front panel from a remote PC.

Internal storage holds as many as 20 waveforms and 20 setups. To store even more information, you can attach a USB memory stick to the frontpanel USB-device port. You can access all important controls and menus from the front panel with a single button press. Pressing the associated knob resets any trace position or offset. Pressing the volts/division knob switches between fixed and variable gain; pressing the time/division knob switches among zoom modes. Buttons on the front panel that open and close menus or switch among modes are backlit so you don't have to guess at the scope's operating mode.

The 40-MHz unit sells for \$695. Prices for the new fourchannel models range from \$1690 for 60-MHz bandwidth to \$2790 for 300 MHz.

-by Dan Strassberg

LeCroy, www.lecroy.com.

Affordable, easy-to-use WaveAce scopes now include four-channel models with bandwidths of 60 to 300 MHz and a two-channel, 40-MHz unit with a US list price of \$695.

# pulse

#### Tighter binning yields more consistent HB LEDs for indoor apps

Wendors of HB LEDs (high-brightness lightemitting-diodes) make white HB LEDs by dosing a blue LED with a blob of phosphor that emits white light when blue light illuminates it. If cost were no object, a manufacturing process could precisely control the LED chip/ phosphor combination to get a consistent white-light color

temperature, but that level of control is prohibitively expensive. However, HB-LED vendors do provide LEDs that fall within certain color ranges, or bins, in a binning process.

If your end fixture uses multiple LEDs, a common design technique for outdoor lights such as streetlights, the lighting will be consistent as the LEDs' color temperature averages out. However, some indoor applications lack the space to allow for multiple LEDs. Applications such as track lighting, spotlights, and can lights may use one HB LED, and the variation in light color temperature can be

visible-as well as irritating. Aiming at such applications, Cree recently announced EasyWhite bins in 3500, 3000, and 2700K color temperatures that are 75% smaller than standard color regions. Cree then uses EasyWhite LED chips in its multichip XLamp MC-E LEDs to obtain a more consistent white color temperature in a single LED package, which can serve as a replacement for 20 to 35W halogen light bulbs in indoor applications such as accent, track, and pendant lighting. The XLamp MC-E EasyWhite LED, at 3000K CCT (correlated color temperature), can produce as many as 560 lumens at 700 mA. EasyWhite LEDs cost about 15% more than Cree's standard-bin LEDs.

-by Margery Conner Cree, www.cree.com.

Cree's EasyWhite bins come in 3500, 3000, and 2700K color temperatures and are 75% smaller than the ANSI C78.377-standard color regions.

#### OPEN-SILICON ADDS SILICON LOGIC ENGINEERING

SOC (system-on-chip) design now has two distinct flows. One flow creates a platform design: a completely new SOC to serve a new application. The other flow slightly modifies the platform to create a derivative design. The derivative flow exploits the platform as much as possible, sometimes just replacing one block in the physical design without changing the rest of the chip at all.

The platform team contains the application specialists, architects, verification gurus, and new-design troubleshooters. The derivative team, perhaps unfairly, can look like a group of routine implementers-that is, they can look dispensable. So the derivative teams are vulnerable to outsourcing.

That's where Open-Silicon enters the picture. The company's founders originally conceived it as a design shop for turnkey back-end-ASIC design, with management and technical customer relations in the United States and a sophisticated back-end process in India. That model was highly successful in good times, and Open-Silicon built a strong customer base among fabless start-ups. In hard times, however, start-ups aren't the best folks to have in your accounts-receivable ledger. Naveed Sherwani, company president and chief executive officer, set out to build a base among larger companies, just as the larger companies started looking to outsource their

derivative-design efforts.

The result is that Open-Silicon now finds itself doing significant business in executing derivative designs. This transition required additional expertise. "To do derivative chips successfully, you need to have front-end design expertise," Sherwani says. The derivative team has to know the platform well enough to grasp the implications of the changes, which can go two or three levels into the platform.

Initially, Open-Silicon met this need by gathering a cloud of specialist design partners to assist them. Sherwani also felt that the company needed in-house expertise at the architecture level and RTL (register-transfer level). "It really helps to be involved in the original platform design or at least to have the experience to understand it," he says.

Eventually, Open-Silicon bought Silicon Logic Engineering, a full-range chip-design team. Now, relying on its newly acquired architecture, RTL, and implementation team, Open-Silicon can engage fully with a platform design, either during its development or later on, and produce derivatives to spec.

For more on this development, go to www.edn. com/100204pa.

-by Ron Wilson Open-Silicon, www. open-silicon.com. Silicon Logic Engineering, www. siliconlogic.com.

# Analog Devices: enabling the designs that make a difference in people's lives.

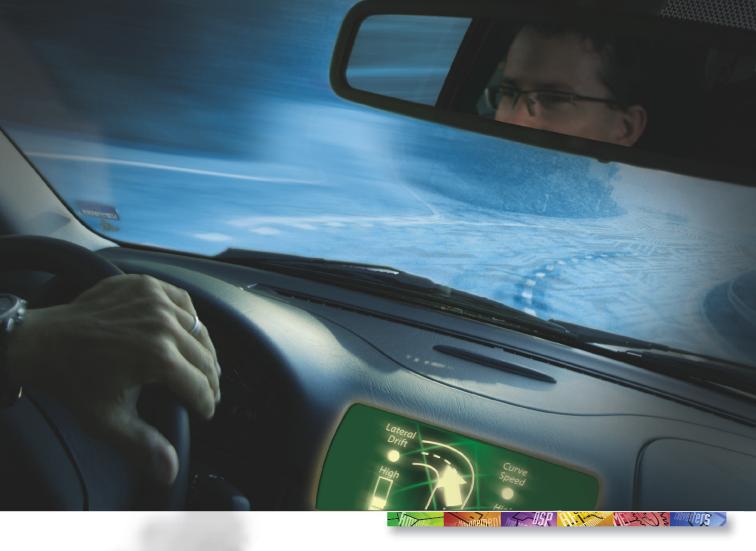

Blind spot sensors and airbag deployment are just two of many critical safety systems enabled by ADI technology. **Each generation of automobiles is safer and more responsive than the last.** Enabled by advanced sensor, measurement, and monitoring technologies, today's automotive electronics gives drivers unprecedented control over their vehicles, making the roads safer for all. At ADI, years of working closely with designers of these electronics systems have yielded signal processing solutions that made adaptive cruise control, lane departure warning systems, stability control, and assisted braking systems standard equipment on many vehicles. When demanding applications require innovative signal processing, automotive engineers turn to ADI. Learn more at *www.analog.com/makeadifference*.

SIGNAL INTEGRITY

#### BY HOWARD JOHNSON, PhD

#### Way too cool

n mid-2005, the Hilton family of hotels mandated installation of the official Hilton Family Clock Radio in 250,000 rooms. This wonderful labor-saving device was designed to rectify two long-standing problems at the hotel: the tendency of guests to foul up traditional clock-radio settings and the burden imposed on hotel staff of checking and maintaining the correct time.

Hilton's clock designers overcame the first difficulty with four buttons atop the unit. These buttons are preset to radio stations that local hotel management selects. With this design, you can wake to one of the hotel's stations, the buzzer, or nothing. No longer can pesky hotel guests leave the

machine inadvertently dialed to an alternative radio station or white noise (my personal favorite wake-up sound).

Regarding the timemaintenance burden, careful studies of clock inaccuracy must have implicated those same pesky hotel guests. I can

just imagine the hotel's management, red-faced and furious, demanding that guests be forever barred from messing up the otherwise perfectly good timekeeping technology provided to them. In response, the designers removed all user-accessible time-adjustment controls from the new clock.

There is no little "time" switch on the back, no pinhole for a paper clip, and no combination of buttons that can adjust the time. Only a certified hotel maintenance engineer can adjust it. The engineer must physically access the clock, remove a Phillips screw near the top on the back, pop off the lid, and depress the "time" button inside to make the adjustment. It's a slow process.

The "no user-accessible controls" strategy requires that the clock be made superaccurate; otherwise, the extreme maintenance hassle of mak-

ing even occasional adjustments would invalidate the new clock's entire *raison d'être*. Toward that end, the developers equipped the clock with a precise internal time reference and a computer-controlled feature that automatically adjusts for daylight-saving time. The

clock is so smart and so accurate that, in the opinion of its designers, it never requires adjustment. Initial user reviews said things like "Best clock ever made by man" and "Nice features, easy to read."

Fast-forward to Sunday, Oct 30, 2005. That day, hotel guests all across Arizona missed their flights. Arizona does not observe daylight-saving time, yet the Hilton family clocks in Arizona hotels did. Early Sunday morning, all the new clocks "fell back" precisely one hour, according to their programming, and all the guests woke an hour late. Needless to say, panic ensued. A month later, when I visited a Hilton family hotel in Tucson, AZ, the hotel building engineer still wasn't finished changing all the clocks. He said, "We'll be done in about six months." Official word from Hilton headquarters came down that the problem affected only some states, and those states would still be required to use the new clocks.

Fast-forward again to March 11, 2007. During that year, Congress changed the daylight-saving-time law in the United States to a different day than previously. Most Hilton family clocks in the United States now require major engineering maintenance four times a year.

Am I making a point? Anyone who ships product to a vast number of installations covering a wide range of application scenarios can tell you what I am talking about. Unanticipated effects always crop up in the field.

This winter, we as a nation found out that incandescent traffic lights emit plenty of infrared heat through the colored lens—enough to melt drifting snow that otherwise would accumulate, obscuring the lens. Wonderful new, energy-efficient LED traffic lights do not emit that much heat (**Reference 1**).

Bad clocks just make people late. LED traffic lights clog with snow, become indiscernible, and cause fatal traffic accidents.

Rapid adoption of large-scale societal change is a bad idea. For example, when our government talks about nationwide health care, I think we should try it for a while in one state first to see whether it works. How about, say, Massachusetts?EDN

#### REFERENCE

Saulny, Susan, "LED Signals Seen as Potential Hazard," *The New York Times*, Jan 1, 2010, www.nytimes. com/2010/01/02/us/02lights.html?sr c=twt&twt=nytimes.

# Where power is hard to find, Tadiran has the solution.

PROVEN 225 YEAR OPERATING LIFE

Don't let the cost and inconvenience of hard-wired AC power send you up a tree. Instead, be as remote as you want to be with the ONLY lithium cells to offer *PROVEN* 25-year service life without recharging or replacing the battery. When it comes to wireless power solutions, Tadiran is taking innovation to extremes.

Tadiran Batteries 2001 Marcus Ave. Suite 125E Lake Success, NY 11042 1-800-537-1368 516-621-4980

www.tadiranbat.com

CONTROL NGINEERING. design

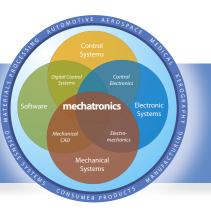

**MECHATRONICS INDESIGN** FRESH IDEAS ON INTEGRATING MECHANICAL SYSTEMS, ELECTRONICS, CONTROL SYSTEMS, AND SOFTWARE IN DESIGN

# Looking beyond STEM

Engineers must lead in innovation, but STEM is only part of the solution.

A s the year and decade end, I see more and more emphasis from K–12 education and private/public funding agencies on STEM (science, technology, engineering, and mathematics) activities. STEM initiatives seem to be the focal point now for addressing the innovation crisis in the United States. While I agree this emphasis is essential, I believe the focus is too narrow and exclusionary. Let me explain.

We are in competition with the entire world, and the innovation crisis we find ourselves in has been fueled by a crisis in education, not only K–12 education but university education, as well. Most students focus on facts, tests, and grades and fail to understand concepts and processes. The inability of graduating students to integrate all they have learned in the solution of a real-world problem, at any level, is a failure. The main goal of education at all levels must be to create critical-thinking problem-solvers and teach them that society's problems are complex and multidisciplinary.

Jon Jensen, associate dean at Marquette University and K–12 outreach director, makes the point that we are a nation of assessors and somewhat obsessed with comparisons, particularly with other nations. Our youth seem to lag behind other countries, most notably in the STEM areas. He says we actually do better as a country than most think, and while we do have a great educational system, we still have a long way to go.

If I am a student with no interest or particular talent in STEM activities, I feel irrelevant to solving the innovation crisis. If I am a teacher in a non-STEM area, I also feel irrelevant. Students as early as the fourth grade are segregated into a college-bound STEM track and the "other" track, the irrelevant one. Parents feel frustrated that their children are not valued for their individual abilities and passions when they do not conform to the perceived valued path as indicated by the proliferation of STEM charter schools and programs.

The STEM disciplines alone will never solve the innovation crisis. As we engineers know, they are only a part of the solution. Innovation—the process of inventing something new, desirable, useful, and sustainable—happens at the intersection of technology (is it feasible?), business (is it viable and sustainable?), human factors (is it desirable?), and complexity (is it usable?). In addition, basic science, mathematics, and engineering skills have become commodities worldwide and are available elsewhere at a fraction of the cost here. Yes, critical-thinking problem-solvers from all disciplines working together are the key to innovation. Innovation is local. You don't import it and you don't export it; you create it. It is a culture. It is a way of thinking, communicating, and doing.

STEM students and teachers, together with students and teachers from the humanities, arts, social sciences, and business, must all realize they are equal partners in solving the innovation crisis. They each play a vital role and together must be able to identify the needs of people and society, critically think and solve problems, generate human-centered ideas and rapidly prototype concepts,

Kevin C Craig, PhD, is the Robert C Greenheck chair in engineering design and a professor of mechanical engineering, College of Engineering, Marquette University. For more mechatronic news, visit mechatronics zone.com.

integrate human values and business into concepts, manage complexity, work in multidisciplinary teams, and effectively communicate results.

The message to our students must be that they are each vital to solving the innovation crisis, and this message must be delivered early and often and in the context of real-world problems. Students need to set high expectations for themselves, as we set high expectations for each of them. They need to discover their passion and their talents and take ownership for developing those talents knowing that in doing so they will play a vital role in transforming the world we live in. Engineers can make a vital contribution by setting a professional example and giving a real-world context to what young students study. Are you up to the challenge? We all know amazing things happen when together we attempt the seemingly impossible! **EDN**

Tune into the latest Mechatronics Webcast—How do you design a military robot?—which will be available ondemand at www.designnews.com beginning Feb 19, and be sure to visit the Mechatronics Zone for the latest mechatronics news, trends, technologies, and applications at www.mechatronicszone.com.

When it comes to creating your next embedded system, an important decision awaits you. Memory. Your design needs speed, reliability, performance and capacity to store the code and data your design demands. No problem. Numonyx has the broadest portfolio of parallel and serial NOR, NAND and phase change memory. And we offer extended temperature support with AEC-Q100 certification on many of our products and expanded design versatility with voltage support up to 5V. All designed to deliver a right-fit solution to help you shorten design cycles, reduce development costs and accelerate the roll-out of your next big idea. Find out how Numonyx memory matters for your next design.

Visit www.Numonyx.com/Embedded for free access to the Numonyx Embedded Design Center.

#### <u>NUMONYX® FORTÉ™ SERIAL</u> FLASH MEMORY

| Product Family           | Density Range  | Voltage/Solution |

|--------------------------|----------------|------------------|

| M25P (block erase)       | 512 k - 128 Mb | 3V, single-I/O   |

| M25PX (4KB block erase)  | 4 Mb - 64 Mb   | 3V, multi-I/O    |

| M25PE/M45PE (page erase) | 1 Mb - 16 Mb   | ЗV               |

#### NUMONYX® AXCELL<sup>™</sup> PARALLEL NOR FLASH MEMORY

| Product Family                                | Density Range | Voltage/Solution |

|-----------------------------------------------|---------------|------------------|

| M29W/EW (JEDEC command set)                   | 4 Mb - 2 Gb*  | 3V, page read†   |

| P30/33 (Intel-based command set, sync burst): | 64 Mb - 2 Gb* | 1.8/3V core      |

# Lead the handheld revolution.

With the industry's lowest power usage, and widest range of small packages, it's no wonder Actel IGLOO<sup>®</sup> FPGAs can be found in the latest handheld portable devices. Actel has been designed into smartphones, eBooks, cameras, medical devices, remote industrial monitoring devices, undersea seismic sensors, military radios, and the list goes on.

Actel IGLOO low-power FPGAs bring reprogrammability, design security, integration, small form factor, and live-at-power-up operation to handheld portable applications, all at a very low cost.

Start designing tomorrow's handhelds today with Actel's batterypowered IGLOO Icicle Evaluation Kit.

Download in-depth white papers, watch short webcasts, and get the Icicle Kit at: actel.com/handheld

BY BRIAN DIPERT • SENIOR TECHNICAL EDITOR

CONTINUED

**INNOVATION IS**

A WELCOME

NTRADICTION

ALTHOUGH THE LAST SEVERAL YEARS HAVE SEEN MUCH CONSTRICTION WITHIN THE SEMICON-DUCTOR INDUSTRY, DEVELOPMENT AND IMPLEMENTATION ACTIVITIES IN THE PC AREA HAVE REMAINED COMPARATIVELY BULLISH. X86 VENDORS HAVE VARIOUS PLANS FOR CONTINUING THIS TREND.

391

n mid-2008, when EDN last looked at the broad x86-processor product segment in detail, the world economy was six months into a deep recession (**Reference 1**). Roughly six months later, worldwide economic conditions remained grim (**Reference 2**). Although government officials now claim that the recession is over, key economic indicators, such as the unemployment rate, should deliver underwhelming statistics for some time to come. You might expect, therefore, that the semiconductor in-

dustry would mirror the broader economy's malaise; this scenario has indeed occurred in many technology and product sectors. The x86 CPU business has bucked the general trend, however, as continued R&D investment and resultant new-IC output demonstrate. "Irrational exuberance," a term that former Federal Reserve Board Chairman Alan Greenspan coined in 1996, has thankfully not been evident. However, the microprocessor and core-logic-chip-set suppliers know full well that, with the rapid evolutionary pace of the PC industry, to tangibly slow down in the short term might be sufficient to ensure demise in

the long term. This insight is evident in the continuation of their prerecession momentum.

#### DESKTOP EXPANSION

Recent analyst reports estimate that Intel holds more than 80% of the overall x86 CPU market and an even higher percentage in key product segments, such as mobile systems and servers. The company also has a higher associated R&D budget and more employees than its key competitors. It is perhaps unsurprising then that most of the new- product roll-outs over the past several years have come from Intel. In 2008, the company launched the Core i7 CPU, its initial product employing the Nehalem microarchitecture. Intel has since substantially broadened the Nehalem line, and you must differentiate among silicon platforms and resultant products to comprehend the full scope of the roll-out.

First, recall Intel's "ticktock" productand-process cadence, a term that company President and Chief Executive Officer Paul Otellini used in 2006. Intel aspires to reduce overall risk by making major product and process transitions at AT A GLANCE

Intel hopes to rapidly spread the Nehalem microarchitecture across all desktop-PC segments, whereas Advanced Micro Devices' recent moves are more modest.

The mobile-computer market is particularly robust, and vendors' intense focus on it reflects that fact.

Intel and its competitors disagree on whether a netbook is anything other than a notebook with neutered features

Buying a chip set from your CPU supplier may be not only unnecessary but also unwise.

Servers, cell phones, and TVs round out the picture for Intel's x86 aspirations.

different times. In the "tick" cycle, the company shrinks a product's lithography to the next process node, making only minor feature alterations in the process. The subsequent "tock" step maintains the same process node but implements more substantial product changes.

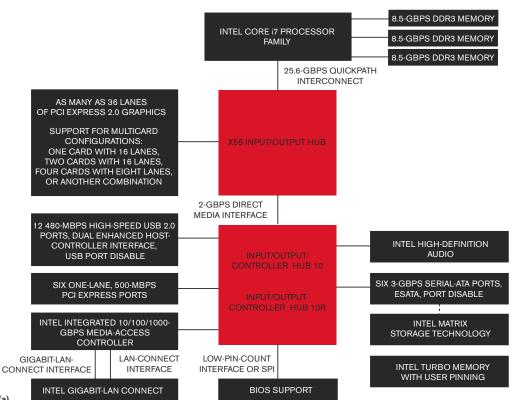

The late-2008 introduction of the Core i7 CPU, a high-end manifestation of the Bloomfield silicon platform, reflected a tock on Intel's 45-nm process (Figure 1). Its innovations versus earlier Core-microarchitecture-based products include three channels' worth of integrated memory controllers; the Quick-Path Interconnect, an AMD (Advanced Micro Devices) HyperTransport-reminiscent core-to-core and CPU-to-CPU mesh; the resurrection of hyperthreading core virtualization; a trilevel integrated-cache architecture; and Turbo Mode, which automatically boosts the clock speed of active CPU cores in situations in which some cores are not in use. maintaining the chip's thermal envelope and boosting overall performance.

Late last year, Intel launched Lynnfield, its second 45-nm, Nehalem-microarchitecture-based silicon tock offering. this time for mainstream-desktop-CPU platforms. Lynnfield discards one of Bloomfield's DRAM channels, instead integrating 16 lanes' worth of PCIe (Peripheral Component Interconnect Express) 2.0 I/O that previously resided in

Figure 1 Intel's first three Nehalem-based CPUs, 45-nm-implemented Bloomfield (a) and Lynnfield (b) and 32-nm-fabricated Clarkdale (c), chronologically reflect a common microarchitecture's migration over time from high- through low-end system configurations.

(a)

a separate north-bridge core-logic IC. The interface to the remainder of the external core logic is also the 2-Gbyte/ sec Direct Media Interface bus; Bloomfield in contrast uses the more-than-10times-faster QuickPath bus. Lynnfield translated into both Core i7 and Core i5 product proliferations; Core i5 disabled hyperthreading support. Intel recently executed its next tick by migrating to a 32-nm process commensurate with the unveiling of the lowend Clarkdale CPU. Clarkdale comes in both Core i5 and Core i3 product flavors; some variants disable not only hyperthreading but also turbo-mode support. Instead of relying exclusively on standalone or core-logic-embedded external graphics-accelerator circuitry, Clarkdale places graphics-processing capabilities alongside the CPU in a multidie, singlepackage arrangement. Clarkdale also migrates the system-memory controller off the CPU and onto the companion die, potentially degrading performance at the trade-off of lower CPU silicon cost. The technology treadmill rolls on; Intel dem-

onstrated its next tock, the 32-nm Sandy Bridge microarchitecture, in functionalsilicon form at last fall's Developer Fofrum. The company showed off a 22-nm test wafer at the same venue.

Intel's primary x86 CPU competitor, AMD, has also over the past several years been fairly busy in this product segment, befitting the company's comparatively strong market-share position in desktop PCs versus other markets. After a problem-plagued roll-out of the 65-nm Phenom CPU in late 2007, complete with poor yields and L3-cache-controller bugs, the subsequent 45-nm Phenom II transition beginning in January 2009 has seemingly gone more smoothly. Phenom II boosts the L3-cache allotment over that of its predecessor and tweaks other minor architectural details. As with Phenom, AMD sells Phenom II not only in full quad-core form but also in triple-core X3 and dual-core X2 variants. These product spins also contain four cores on each die, but AMD disables one or two of them, presumably because they don't pass functional or speed testing. The company is attempting to maximize usable product yield from each manufactured silicon wafer, but this strategy is costly and less than ideal.

Therefore, for mainstream-desktop-PC applications, AMD last summer rolled out the 45-nm Athlon II product line. Whereas the company derived the original Athlon families from the K8 and earlier microarchitectures, Athlon II evolves from the same K10 core foundation as Figure 2 AMD has never been a fan of Intel's "netbook"-naming claims,

of Intel's "netbook"-naming claims, and partner Hewlett-Packard's designs reflect an alternative fiscally sensitive approach (a). Via's Nano CPU is one of three fundamental options for Lenovo's IdeaPad S12; the other two variants pair an Atom CPU with either an Intel or an Nvidia Ion chip set (b).

Phenom and Phenom II. However, as a die-slimming move, AMD offers Athlon II only in dual-core form; the company also deleted Phenom II's L3-cache array, compensating somewhat by boosting the L2-cache allotment. AMD also still sells single- and dual-core, 65-nm Athlon products. More generally, the company has attempted to counterbalance a comparative dearth of fundamental product proliferations through a blizzard of clock-speed and operating-voltage spins, striving to satisfy a plethora of product-per-

#### SERVER SPINS

Desktop and mobile versions of CPU platforms share similar features, and similar commonality exists between desktop and workstation-and-server variants. The workstation-plus-server adaptation typically offers multiprocessor connectivity, undergoes additional testing, and supports memory technologies that are amenable to high system capacities.

For example, the server-tuned version of Intel's Bloomfield is Gainestown-that is, Nehalem EPthe Xeon 5500 series. Intel plans to introduce Jasper Forest, a server variant of the Lynnfield desktop-PC and the Clarksfield mobile-system CPUs. Also on the company road map is Gulftown, a six-core shrinkage of the eight-core, 45-nm-based Beckton-that is, Nehalem EX-to the 32-nm-process node and available in both desktop and dual-processor server versions.

Advanced Micro Devices exhibits similar desktop/server commonality. For example, the 65-nm Phenom desktop and Barcelona server CPUs, respectively, migrated to the 45-nm Phenom II and Shanghai. AMD also has a desktop-PC-targeted variant of its six-core, 45-nm Istanbul server processor on its 2010 road map. formance-versus-price expectations with comparatively few silicon foundations.

#### **MOBILE MIGRATION**

As anyone who has recently visited computer retailers or scanned their advertisements realizes, desktop-computer sales are at best stagnant, whereas mobile-computer sales are exploding. Intel reportedly controls approximately 90% of this market, so it's no surprise that the company has focused significant attention in this area. Most Intel-based notebook computers still use so-called CULV (consumer-ultralow-voltage) CPUs employing the previous generation's Core microarchitecture, although the company last fall began shipping mobile Core i7 CPUs it derived from Clarksfield, a notebook-intended variant of the Nehalembased Lynnfield. More recently, Intel unveiled Arrandale, a mobile version of Clarkdale. The current modern differentiation between desktop and mobile CPUs is nebulous at best. It reflects operating-voltage and clock-frequency variations but little if any underlying circuitry differences because power consumption is a critical consideration in all market segments (see sidebar "Server spins").

To date, AMD has not attempted to aggressively shoehorn Phenom, Phenom II, or Athlon II CPUs into notebook computers, relying instead on power-consumption-optimized earlier-generation Athlon products. The company prefers to promote and sell them in processor-plus-chip-set form. Take, for example, the Neo platform, which AMD unveiled at the January 2009 Consumer Electronics Show along with system partner Hewlett-Packard (**Figure 2**). AMD, by virtue of its 2006 acquisition of ATI Technologies, now touts formidable stand-alone and core-logic-integrated graphics capabilities. And AMD isn't shy about pointing out its claimed advantages over Intel's alternatives as they relate to such topics as Windows Vista and Windows 7 UI (user-interface) enhancements, mainstream 3-D gaming scenarios, and increasingly important hardware-assisted decoding of leading-edge video codecs.

Via Technologies, meanwhile, has unveiled three variants of its latest-generation, 64-bit, singlecore Nano CPU. The 1000 and 2000 series of products are identical from the silicon and micro-

code standpoints; the only differentiation is with respect to the marketing moniker. The newer 3000 series, on the other hand, represents a more involved circuit redesign, adding support for SSE4 single-instruction/multi-(streaming ple-data extension version 4) and with claimed higher performance and lower power consumption. The long-promised dual-core variant of the Nano family remains absent; the latest company road maps forecast its arrival to occur no earlier than mid-2010. Nonetheless, Via has secured several design wins with Tier 1 notebook-PC OEMs, such as Lenovo

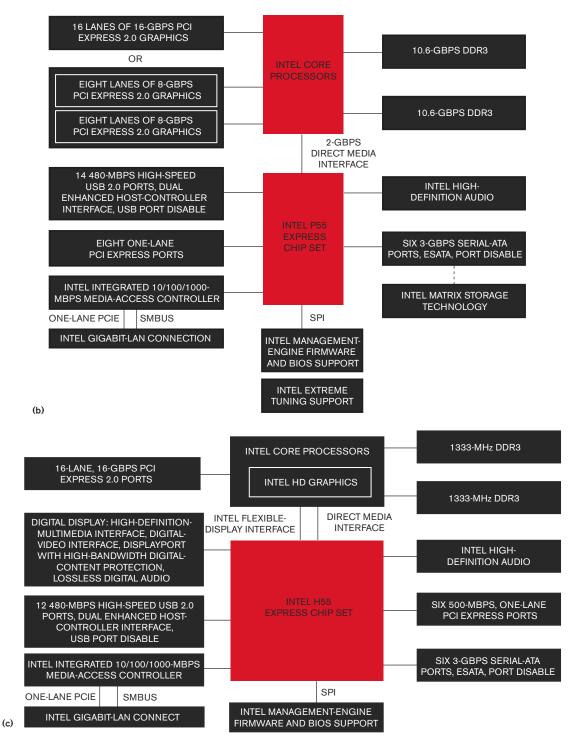

Figure 4 Nvidia's Ion companion chip has sufficient video-decoding capabilities to transform the Atom CPU into a passable home-theater-PC foundation (courtesy Acer).

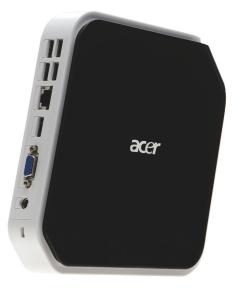

Figure 3 Selective integration within the CPU is the hallmark of the Diamondville-to-Pine Trail Atom evolution of 2008 (a) versus today (b), although Intel may be the key beneficiary from a competitive isolation standpoint.

and Samsung. Via also continues to sell its earlier-generation C7 processors.

#### **FISCAL EVOLUTION**

The term "netbook" represents Intel's attempt to separate the systems from notebooks (see sidebar "Handsets and other CE hopes"). Netbooks contain low-cost Atom microprocessors, whereas notebooks include higher-end, higherprofit, and higher-revenue-garnering Intel CPU alternatives. A third category, the smartbook, includes 3G (third-generation) cellular-data subsystems and often offers carrier subsidization. Processor differences aside, Intel and partner Microsoft have undertaken other netbook-versus-notebook differentiation steps. These steps include restricting to 2 Gbytes the maximum system memory that the associate core logic supports, encouraging their customers to further decrease the installed system memory to 1 Gbyte, and constraining the screen sizes and resolutions that netbooks can implement. Historically, Microsoft's motivation has been to minimize the number of less lucrative Windows XP licenses that it sold into netbooks versus those for the more fiscally attractive Windows Vista in notebooks. Nowadays, its intention is to steer as many licensees as possible away from the netbook-tailored Starter Edition of Windows 7 and toward more expensive variants of the OS.

Intel in December formally unveiled the latest Atom CPU, Pineview—or Pine Trail in CPU-plus-chip-set-platform lingo—which exemplifies this segmentation trend (Figure 3). Pineview integrates the graphics core and memory controller that the earlier-generation Diamondville device implemented on a separate north-bridge core-logic IC. Pineview's approach has battery-life advantages, especially when you consider that the earlier 90-nm-process-based 945GC and 130-nm ICH7 consumed far more power than did the 45-nm-derived Atom N- and Z-series CPUs.

However, Intel also implemented the Pineview Atom CPU on a 45-nm process, which translates to an increase in transistor count over precursor Atom CPU generations. To minimize die size, Pineview's graphics core has fewer features than that of the 945GC. This seeming step backward may make you wonder why else Intel might have made this integration move. Performance is a likely reason; although the CPU core itself remains the same, the tight coupling to the graphics and memory subsystems is preferable to the earlier device's separation through the front-side bus. Also recall that the graphics core employs system memory as its frame buffer. This time around, the device supports 667- and 800-MHz DDR2 SDRAM versus only 533-MHz memory on the 945GC. Unfortunately, Pineview's video outputs have maximum resolutions of only 1366×768 pixels from digital ports and a maximum of either 2048×1536 or 1400×1050 pixels with an analog VGA connection.

#### **CHIP-SET COMPETITION**

Pineview's tight coupling between the CPU and the GPU (graphics-processing unit) also conveniently—at least

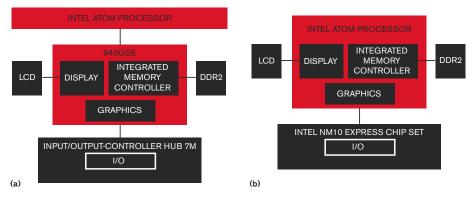

#### HANDSETS AND OTHER CE HOPES

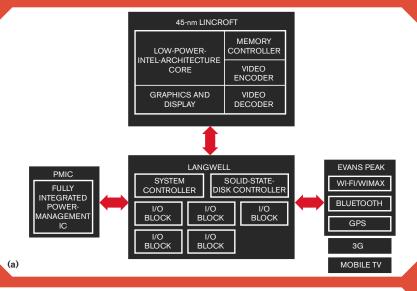

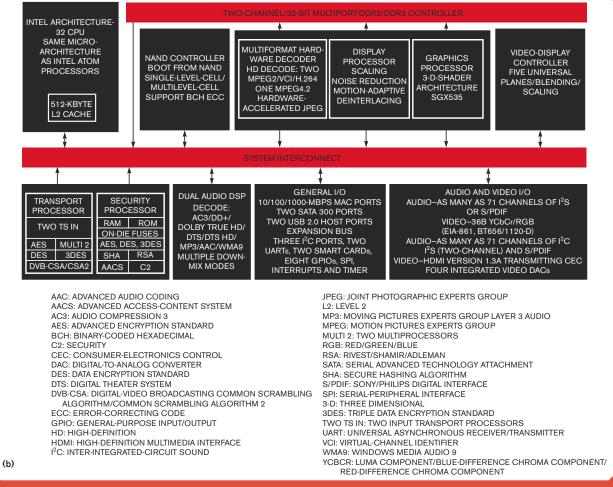

Although Intel's aspirations to seriously combat ARM and MIPS in the **CE** (consumer-electronics) market have to date largely gone unrealized, the company strives onward. Coming later this year is Moorestown, a handheld-device-focused platform follow-on to the first-generation Atom Silverthorne (Figure A). As with Pine Trail for netbooks, Moorestown's CPU remains on the 45-nm-process node but is more integrated than its precursor. Also, at last fall's Intel Developer Forum, the company unveiled the Atom CE4100, a highly integrated descendant of the Pentium M-based CE3100 initial offering, targeting use in set-top boxes and network-enabled TVs.

Figure A Intel hopes its Moorestown two-chip set will lead to some serious cell-phone design wins (a), whereas the Atom CE4100 targets the living room (b).

for Intel—shuts out third-party graphics products, which previously connected to the Atom processor through that same front-side bus. Instead, third-party graphics chips must tether to Pineview through the NM10 companion chip's PCIe lanes, several bus "hops" away from the processor. System memory, which such a GPU might prefer to also employ as its frame buffer, is also several hops away, resulting in either poor performance or the necessity for a costly dedicated frame buffer that directly connects to the third-party GPU.

Pineview's integration, reminiscent of that in the Clarkdale and Arrandale CPUs, brings to the forefront a longstanding feud between Intel and Nvidia (Reference 3). Nvidia's Ion chip, an alternative to Intel's two-chip 945GCplus-ICH7 approach, muddles the distinction that Intel strives to preserve between netbooks and notebooks. Ion uses the same IC that Apple's latest Intelbased MacBook laptops and entry-level Mac mini desktop computers use. It has secured a few key design wins in portable systems alongside Intel's first-generation Atom CPUs, as well as in a host of socalled nettops for home-theater-PC and other niche applications (Figure 4).

Ion's fundamental appeal, aside from its single-chip function integration, is that it has notably better graphics- and video-processing capabilities than Intel's alternative. Ion offers some degree of hardware-accelerated decoding for advanced video-compression algorithms, such as H.264, which Adobe Flash is adopting, and VC-1, which Netflix's Watch Instantly online service employs. Blu-ray discs also use both H.264 and VC-1; Ion handles most of the processing itself instead of burdening the CPU with the task. Nvidia has long publicly complained, however, that the Atom pricing strategy is competitively unfair in that Intel charges significantly more for the stand-alone CPU than when it sells it with the 945GC and ICH7. Indicating the potential reality behind Nvidia's claim, systems based on Ion tend to be significantly more expensive than their "generic" Atom counterparts. It's unclear, however, whether this differentiation reflects bill-of-materials costs or PC OEMs' desires to use potential customers' perception of the superiority of an Ion-inclusive system to boost its price.

+ Go to www.edn.com/100204df to post a comment on this article.

Speaking of pricing, even if Nvidia figures out how to make a cost-effective offering with compelling performance with its upcoming Ion 2 chip for Pineview, the product's success isn't assured. Pineview alone has sufficient graphics horsepower to run Windows 7's rich GUI (graphical user interface), for example. You may thus conclude that video is the primary motivation to append Ion 2 to Pineview. An even more costeffective silicon alternative exists, however, in Broadcom's Crystal HD (highdefinition) video-decoder IC. The company initially unveiled the device several years ago, but it has only now hit its stride in conjunction with the ascendancy of the Atom CPU. Intel prominently showcases Crystal HD in its Pineview promotional materials. And OEMs sell Crystal HD-augmented systems for only \$30 or so more than their Atom-only counterparts, suggesting that Broadcom is aggressively pricing the part to carve out a market and fend off the Nvidia alternative. To buffer itself against Atomonly business dependence, Nvidia also plans to develop Ion variants for use with Via's Nano CPU series.

#### **CONSUMER PROTECTION**

Ion is only one of several areas of disagreement between Intel and Nvidia. Nvidia also has yet to obtain a license for either the QuickPath Interconnect or Direct Media Interface buses, meaning that the company cannot legally sell chip sets for Nehalem-generation Intel microprocessors. More generally, Nvidia is struggling from a business standpoint, with its DirectX 11-supportive graphics chips notably delayed and with AMD's microprocessor customers also tending to select AMD/ATI chip sets and discrete GPUs.

The disputes between the two companies are among several motivations that the US FTC (Federal Trade Commission) mentioned when in mid-December it filed a lawsuit against Intel for alleged anticompetitive practices. This latest legal setback is only one in a series that Intel has suffered in the past year. The European Union also last May fined Intel \$1.45 billion, which the company agreed to pay, although it vowed to appeal the ruling. In November, New York State filed an antitrust lawsuit against Intel, and Intel in the same month paid AMD \$1.25 billion to settle long-standing litigation between the two companies.

Nvidia may be closely following the evolution of the FTC action for more reasons than concern about chip sets and graphics. An unconfirmed longstanding rumor suggests that the company has for some time been internally developing an x86-microprocessor architecture. Both design-team acquisitions and official-albeit obscure-company comments bolster this rumor. However, Nvidia has not yet obtained permission to sell chips employing the architecture. If the x86-by-Nvidia rumor is true and if the FTC's legal aspirations are successful, one possible remedy would be for the FTC to require that Intel grant Nvidia an x86 license.EDN

#### REFERENCES

Dipert, Brian, "Embedded x86: keystone of your non-PC design?" *EDN*, May 29, 2008, pg 38, www.edn.com/ article/CA6562580.

Dipert, Brian, "Evaluating value-oriented x86 CPUs: the price of falling prices," *EDN*, Jan 8, 2009, pg 30, www. edn.com/article/CA6625435.

Dipert, Brian, "CES 2009: the price of falling prices and a path to Intel's potential demise," *EDN*, Jan 8, 2009, www.edn.com/article/CA6627620.

#### FOR MORE INFORMATION

Acer www.acer-group.com Advanced Micro Devices www.amd.com Broadcom.com Hewlett-Packard www.hp.com Intel www.intel.com FORMATION Lenovo www.lenovo.com Microsoft www.microsoft.com MIPS Technologies www.mips.com Nvidia www.nvidia.com Samsung www.samsung.com Via Technologies www.viatech.com

You can reach Senior Technical Editor Thrus Univer at 1-916-760-0159, bdipert@edn.com, and www.bdipert.com. BY RICK NELSON . EDITOR-IN-CHIEF

# Wireless to

s wireless technology becomes increasingly pervasive, vendors are offering a variety of hardware and software technologies to help you add communications functions to your products. Offerings support communications standards, including Bluetooth, Wi-Fi, GPS (global-positioning system), LTE (long-term evolution), and WiMax (worldwide interoperability for microwave access). Choosing the chips and associated software necessary to add wireless connectivity—

and proving that your chosen implementation works and meets relevant certification requirements—can be challenging, however. Even if you put together a working design, you might not succeed in the market if you haven't optimized performance, power consumption, cost, and size. And what's optimum today might not be optimum as communications standards and your customers' needs evolve, so you'll want to choose a hardware and software implementation that lets you adapt without starting from scratch with each new generation (see sidebar "Wireless at a glance").

Each of your successive generations will also probably need to remain compatible with earlier versions. "A general trend in the industry is that we are adding new standards and protocols but not subtracting the old ones as quickly," says Fanny Mlinarsky, founder and president of consulting company OctoScope, using the cellular industry as an example. "They linger, and we have to be backward-compatible. So as the whole cellular industry is reinventing itself with broadband wireless 3G [third generation] and 4G [fourth generation], it has to carry that baggage of GSM [global system for mobile communications] in Europe and CDMA [code-division multiple access] here. Even WCDMA [wideband CDMA], which is 3G, is barely making it to market now, only to be replaced soon by LTE."

For some applications, you may be able to choose a single chip to implement your wireless links. Marvell at last month's CES (Consumer Electronics Show) touted its Avastar family of wireless connectivity devices for always-on consumer-electronics devices, such as handsets, portable media players, e-readers, printers, digital cameras, netbooks, digital TVs, set-top boxes, DVD players, gaming consoles, and even thermostats. The company can snap together its IP (intellectualproperty) cores to create devices for target markets. It is now sampling devices for Wi-Fi; Wi-Fi and Bluetooth; Bluetooth and FM; and Wi-Fi, Bluetooth, and FM. Marvell expects to introduce four more devices in the family during the first half of this year.

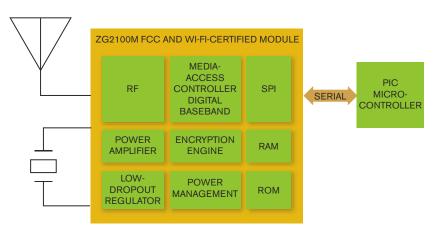

For developers of embedded systems who need to add wireless functions to a microcontroller-based design, Microchip Technology offers one-stop shopping. The microcontroller maker took aim last month at enhancing its support of embedded wireless applications with its acquisition of ZeroG Wireless, a privately held fabless semiconductor developer of Wi-Fi-certified transceivers and FCC-certified modules. Embedded-system designers can use ZeroG devices to add the ubiquitous Wi-Fi networking protocol to any of Microchip's 8-, 16-, or 32-bit PIC microcontrollers through an SPI (serial-peripheral interface).

Microchip supports other wireless standards, as well, including ZigBee. The company announced in December that it has received certification for its new ZigBee-RF4CE-compliant platform, a development kit for Zig-Bee that includes the XLP PIC controller, an MRF24J40 transceiver for 802.15.4 ZigBee networks, and an FCC-certified module. The kit comes with a certified protocol stack for ZigBee applications.

The XLP PIC at the center of the platform integrates several peripherals for capacitive touch sensing, USB interfaces, and analog I/O. Microchip incorporates software, including the mTouch sensing software, in the kit to use the peripherals. Other tools for the kit include the MPLab integrated development environment, MPLab Real ICE system, MPLab ICD 3, Pickit 3 debugger/programmer, and C compilers.

You'll also find single-chip implementations for cell phones. For example, Infineon offers its single-chip X-Gold 116 GSM/GPRS (general-packet-radio-service) implementation, which the company fabricated in 65-nm CMOS, for messaging phones. That chip integrates the GSM baseband, RF transceiver, VENDORS ARE SERVING UP A VARIETY OF HARDWARE AND SOFTWARE FLA-VORS TO ADD COMMUNICA-TIONS CAPABILITY TO FIXED AND MOBILE DEVICES.

power-management functions, SRAM, and FM-radio functions in an 8×8-mm package. Infineon offers the device as

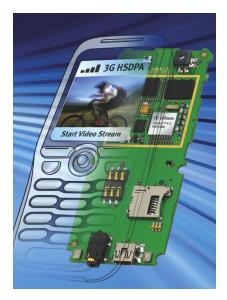

part of its XMM 1160 messaging-phone platform, which incorporates about 50 components on a four-layer printed-circuit board and comes with user-interface, multimedia-framework, media-player, and Java software. The company also offers the XMM 6130 platform, which targets the entry-level Internet-browsingphone market, supporting 3G HSDPA (high-speed downlink-packet access). The platform integrates an ARM11based microcontroller, baseband digital and analog features, and power-management functions, and it offers dedicated interfaces for a camera, a display, a USB port, and memory cards.

Single-chip GPS implementations are available, as well. Atheros Communications last month announced the latest member of its family of GPS products, the third-generation, single-chip AR1520 GPS receiver and companion Atheros FYX 1.0 software suite. Atheros based the AR1520 on the new Atheros FYX location core. It delivers greater navigation accuracy, faster location fixes, enhanced receiver sensitivity, and lower power consumption than the company's previous products. These features make the AR1520 suitable for mobile consumer products, such as PNDs (personal navigation devices), netbooks, smartbooks, portable gaming devices, media players, and smartphones.

ST-Ericsson, meanwhile, is taking a technology-platform approach to meet consumer needs for ubiquitous connectivity. According to Thierry Tingaud, vice president and general manager for 2G, EDGE, TD-SCDMA, and connectivity products at the company, the mobile device has become the convergence point for consumers for multiple wireless technologies, including GPS and Wi-Fi, as well as cellular operation. ST-Ericsson offers platforms for smartphones, feature phones, and entry-level phones as well as platforms for connected devices, such as wireless modems in laptops.

The company announced in December that it is working with Nokia as part of a long-term partnership to de-

#### AT A GLANCE

We are adding new communications standards and protocols but not subtracting the old ones as quickly.

It's not just about making chips; it's also about gluing everything together with software.

An effective way to support multiple communications standards is to employ a technology platform or reference design.

People underestimate how much it costs to put wireless connectivity into a product.

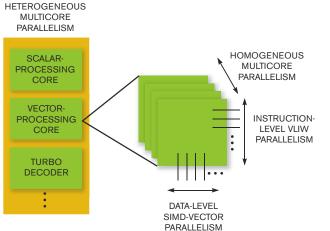

Designers can implement baseband functions in FPGAs and ASICs that they once had to implement in software.